前言

时钟系统的正常运作,才能保证 STM32 稳定的工作。然而 STM32 的时钟系统极其复杂,不像 51 系列单片机一样一个时钟系统就可以解决一切问题。

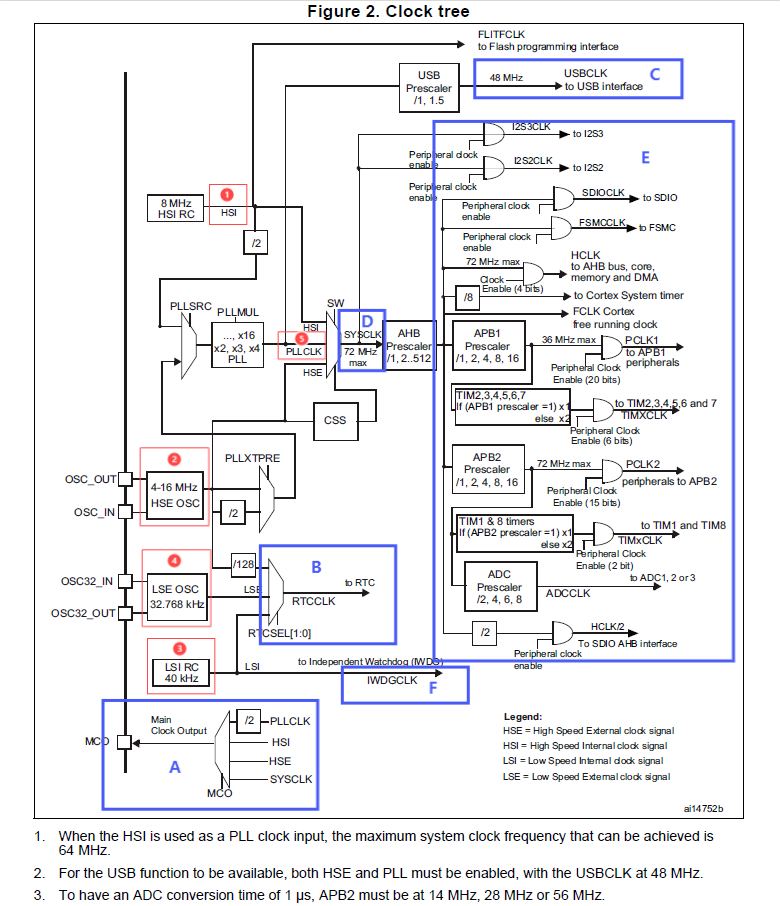

STM32 的时钟系统对于初学者来说并不友好,它像一棵参天大树一样枝叶繁茂,本文致力于分解 STM32 时钟树,使读者清晰了解 STM32 时钟树背后的原理。

STM32F103VE 系列时钟树

1. 时钟树大图

一下是 STM32F103VE 的官方文档给出的时钟系统的结构框图。

2. 时钟源解释

我们可以看出,官方给出的文档里的框图十分的复杂……

但其实可以进行一一的拆解解释。

如 STM32F103VESystemClock 图中红色选框所标出的,系统共有五个时钟源,依次分别是 HSI 、HSE 、LSI 、LSE 和 PLL:

- HSI(High Speed Internal Clock Signal) 高速内部时钟,其由内部的 RC 振荡器发生,频率为 8MHz,但我们都知道 RC 振荡器的精度并不很好,对于此 HSI 来讲,大约的误差在 ±2% 左右。

- HSE(High Speed External Clock Signal) 高速外部时钟,其可外接石英/陶瓷振荡器,或者其他的外部时钟源,频率范围为 4MHz ~ 16MHz。

- LSI(Low Speed Internal Clock Signal) 低速内部时钟,其由内部的 RC 振荡器发生,频率为 30KHz,提供低功耗时钟。我们在此也不难看出,蓝色的 F 选框 - IWDG 独立看门狗就只能使用 LSI 作为时钟源。同时 LSI 还可以作为 RTC 的时钟源使用。

- LSE(Low Speed External Clock Signal) 低速外部时钟,一般外接 32.768kHz 的石英晶体振荡器,是主要的 RTC 时钟源。

- PLL(Phase-locked Loops Clock Signal) 锁相环倍频输出,其时钟源输入如图中所示可以为 HSI/2 、 HSE 或者 HSE/2 。倍频可以选择 2~16 倍,但其输出频率最大不可超过 72MHz 。关于 PPL 锁相环的介绍可以看我的这篇文章 PLL-锁相环

注意: HSE 的引脚(OSC_IN/OSC_OUT) 是独立引出来的,CubeMX 设置好外部时钟源即可直连外部晶振。而 HSI 的引脚(PC14 - OSC32_IN/PC15 - OSC32_OUT)是复用引脚,需要在 CubeMX 做相应的引脚配置。

3. 时钟去向解释

上面我们一一解释了系统的时钟来源,那么这 5 钟时钟源是怎样给各个外设以及系统提供时钟信号的呢?

如 STM32F103VESystemClock 图中蓝色选框所标出的,大致分为六个去向:

- A: MCO(Master Clock Output) 是 SMT32 的时钟输出(PA8 引脚),它可以选择一个时钟信号输出:PLL/2 、 HSI 、 HSE 、或者 SYSCLK 。这个时钟可以用来给外部其他系统提供时钟源。

- B: RTC(Real_Time Clock) 实时时钟,其可以选择 LSI 、 LSE 、 或者 HSE/128 。

- C: 全速 USB 模块,其串行引擎需要频率为 48MHz 的时钟源。该时钟源只能从 PLL 输出端获取,可选择为 PPL 或 PLL/1.5。所以当使用 USB 模块时,PLL 必须使能且对应频率为 48MHz 或 72MHz。

- D: SYSCLK 系统时钟,它是 STM32 绝大部分模块的时钟源。系统时钟可以选择为 PLL 、 HSI 、 HSE 。系统时钟默认最大为 72MHz ,当然也可以超频,不过就像电脑的 CPU 超频一样也会出现一些问题(时序紊乱、程序跑飞、芯片发热烧掉等)。

- E: 其他外设,从上图可以看出,基本其他的外设都来源于 SYSCLK。 SYSCLK 通过 AHB 分频器分频后送给各个模块使用。包括:AHB 总线、内核、内存和 DMA 使用的 HCLK 时钟; /8 分频后送给 Cotex 的系统定时器时钟,即 systick ;直接送给 Cortex 的空闲运行时钟 FCLK ;送给 APB1 分频器,其输出一路供 APB1 外设使用(PCLK1 ,最大频率 36MHz),另一路送给定时器 2、3、4、5、6、7 使用(TIMXCLK);送给 APB2 分频器,其输出一路供 APB2 外设使用(PCLK2,最大频率 72MHz),另一路送给定时器 1、8 使用(TIMxCLK),第三路通过 ADC 预分频器送给 ADC1、2、3 使用(ADCCLK ,可分频 /2 、/4 、/6 、/8)

- F: IWDG 独立看门狗定时器,其只能选择 LSI 作为时钟源。

APB1和APB2的区别:

APB1(Advanced Peripheral Bus 1) 是低速外设总线,其最大允许频率为36MHz。它主要负责连接低速外设,如 DAC 接口、备份接口、CAN 接口、I2C 接口、USART 2-5 接口、SPI 2-3 接口、窗口看门狗等。这些外设通常对时钟频率要求较低,因此被归类为低速外设。

APB2(Advanced Peripheral Bus 2) 是高速外设总线,其最大允许频率为72MHz。它主要负责连接高速外设,如 USART1 接口、SPI1 接口、定时器 1 接口、ADC1 和 ADC2 接口、端口 A-E 时钟使能、辅助功能 IO 时钟使能等。这些外设通常对时钟频率要求较高,因此被归类为高速外设。

总结

本文主要对 STM32 时钟系统进行解释,我们从原理框图入手,解释时钟线路的来源和去向,STM32的时钟十分复杂,希望各位能够反复阅读,内化于心,这样在以后的 STM32 开发以至于其它高性能 SOC 的学习中才能游刃有余。

学路漫漫其修远兮,吾将上下而求索